Processor Design Part 1

The project specs for lab07 and project05 provides high-level requirements. This guide, along with lecture material, will drill down into the details. Using all of this information, you will implement and simulate a single-cycle RISC-V processor in Digital.

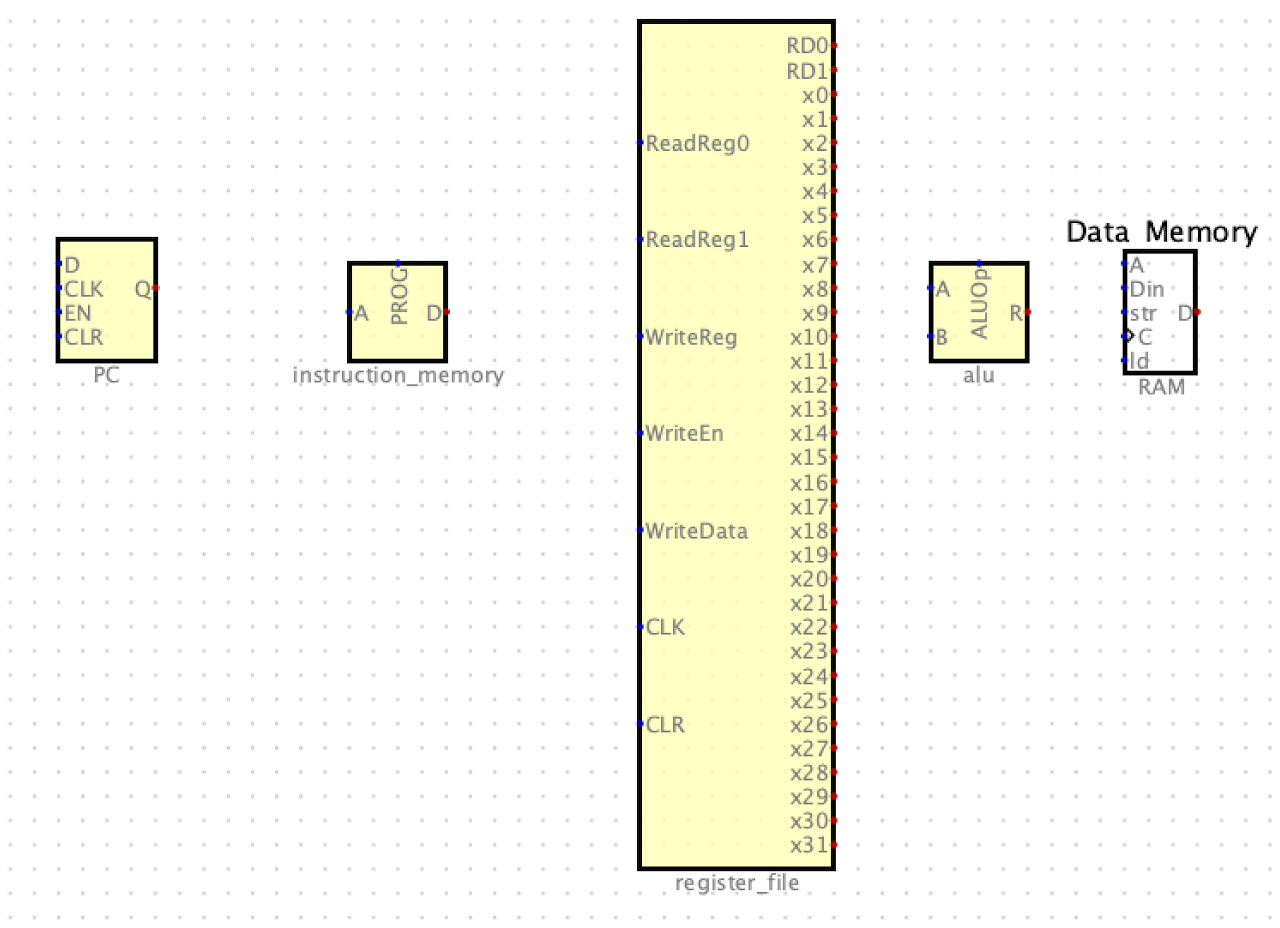

Major Components

- The PC register will hold the address of the instruction we are currently executing

- The Instruction Memory holds the machine code representation of our test programs , including the unimp marker instruction

- You will use the hex output from makerom3.py as input into instruction memory

- The Register File supports reading and writing from RISC-V registers. We will expose the register values as outputs, so they may be used as inputs to other circuits

- The Arithmetic Logic Unit (ALU) supports addition, subtraction, multiplication, logical shift left, and logical shift right. We will also use the ALU to computer branch target addresses and memory target addresses.

- The Extender supports sign-extension of immediate values.

- Data Memory is a Digital RAM component which supports our simulated stack, storing function parameters and preserved register values, as needed.

PC

- We will represent PC using a Digital Register component, in the top level of our processor

- Digital does not provide a CLR input to its registers, but we can add one as our project grows

- EN will always be 1 so we can move the PC forward 4 bytes on each CLK cycle

- As in Project04, you will update the PC with a calculated address for JAL and JALR instructions

- The D output will address the Instruction Memory to retrieve the instruction word at the PC address

Instruction Memory

- Instruction memory will be built out of Digital ROM components, starting with one and expanding to more for each simulated function

- Each RISC-V machine code instruction is 32 bits, so the ROM will have 32 data bits

- The number of address bits will vary based on the size of your simulated programs. Recall that with 8 address bits, you can address 2^8 = 256 instructions

- Similar to Project05, note that the ROM is addressed by 32-bit words, but the PC represents a byte address. You can obtain the word address using a splitter

- You will use makerom3.py to generate a .hex file which can be loaded into the ROM.

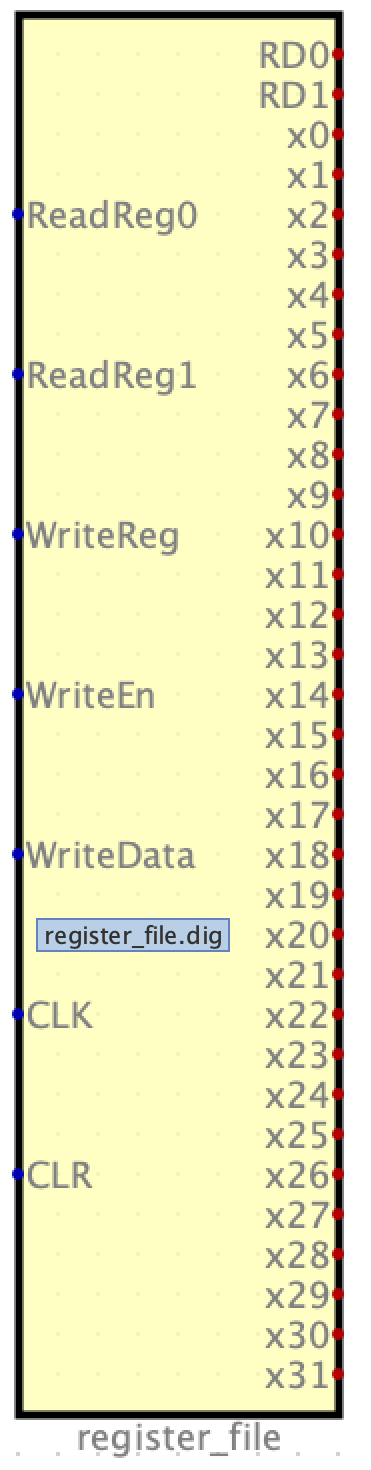

Register File

- You will create a circuit which supports reading from two registers and writing to one register in the same clock cycle.

Inputs

ReadReg0(5 bits) selects the register value to output onRD0ReadReg1(5 bits) selects the register value to output onRD1WriteReg(5 bits) selects the destination register to updateWriteEn(1 bit) determines whether we will update a register in this clock cycleWriteData(64 bits) contains the value we will write toWriteRegifWriteEnis highPC(64 bits) contains the value of the program counterCLK(1 bit) is the clock input from the top-level clock componentCLR(1 bit) allows the register values to be set to zero on a clock tick

Outputs

RD0(64 bits) contains the value of the register specified byReadReg0RD1(64 bits) contains the value of the register specified byReadReg1x0-x32(64 bits) are outputs for the 32 registers- You should use these as inputs to tunnels which are used to build the dashboard on the top-level circuit.

- You should also reflect

PCandPC+4on the dashboard using tunnels, since that will be useful for debugging branch calculation

Arithmetic Logic Unit

- The ALU is a combinational logic component. It does not hold state like sequential logic components, so it does not need a CLK input.

- Data processing instructions use addition, subtraction, multiplication, logical shift left, and logical shift right.

- Load/store memory instructions use addition and subtraction to calculate target memory addresses

- Branch instructions use addition to calculate the target branch address

Inputs

- A (64 bits) is the first ALU operand

- B (64 bits) is the second ALU operand

- ALUop (3 bits) selects an ALU operation:

- 0b000: add

- 0b001: sub

- 0b010: mul

- 0b100: sll

- 0b101 srl

Outputs

- R (64 bits) is the ALU result

- If you need your ALU to support more operations, you may need to add more selector bits and connect those to the Control Unit

Initial Top-Level Circuit

- This starter circuit gives you a general idea of how to start.

- It can execute some instructions, with manual help from you.

- In order to play with it, you can put instructions into the ROM, and manually enter the RR0, RR1, and WR inputs to the Register File and ALU.

- Of course the Control Unit is the big missing piece, which we will discuss separately.

- Wire up PC = PC + 4

- Wire explicit inputs to all components

- Add tunnels and probes to see register state